Uošte mi nije jasno kako se rangiraju memorije sa različitim brzinama i latencama. Jasno je da je bolja brža memorija sa manjom latencom, ali šta kada su statistike šarene (sporija a niže latence ili brža a više latene)?

Naiša sam na dve formule koje uzimaju ove dva podatka u obrzir (CL*2000/brzinom i CL/brzinom*1000) što je u suštini ista stvar.

Da li je ovo tačno?

Evo rezultata prema tim formulama za memorije iz gornje Samsung Single sided B-die:

Pogledajte prilog 245304

Po ovome se vidi koje su brže ali verovatno nije srazmerno. Ali me tu bune onda rezultati sa

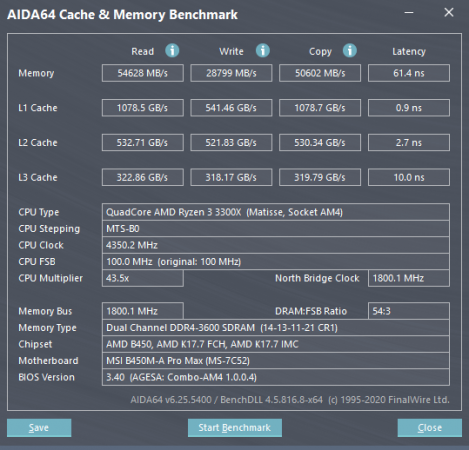

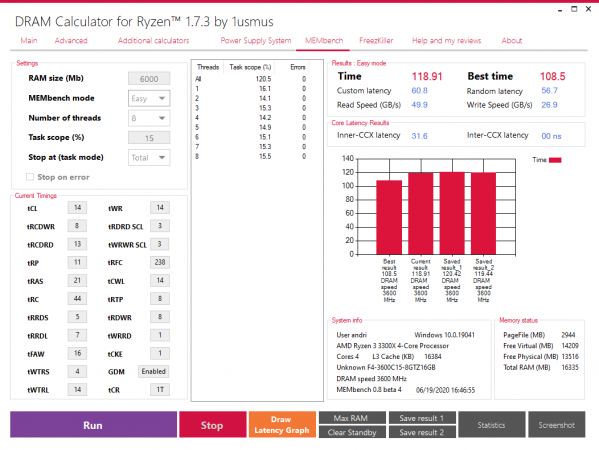

ovog linka, gde bi po formuli 3200C14 trebala biti brža od 3600C16 ali to ovde nije slučaj. Ili sa

ovog linka gde bi trebalo da je 3200C12 brža od 3466C14 ali je obrnuto.

rangiraju se tako da se svaka memorija proizvodi po odredjenom standardu, kao i sve ostalo na svetu.

mala digresija bi bila da je memorija retko kada ( skoro nikada, sem ako se radi o sistemu koja koristi integrisanu grafiku ) usko grlo prosecnoga sistema.

rangiranje memorija se vrsi verovatno po kvalitetu istih u najzahtevnijim procesima koje iziskuju memoriju koja u najkracem odzivu isporucuje najvecu ( uvek tacnu ) kolicinu informacija koje su predhodno u njoj zapisane, tj nemaju gresku izmedju ( TACNO) zapisane i ( TACNO )ocitane vrednosti ( NIKADA )

serverske konfiguracije pretezno koriste najbolje memorije jelte, i gle cuda one rade pretezno na nazivnim frekvencijama za odredjeni ( JEDEC ) standard ( ddr ddr2 ddr3 ...) pa su jos i ECC

(JEDEC ) standardi definisu pored frekvencija i latencije memorija, a ako frekvencije " ispadaju " iz standarda ( overclock ) desava se da to ide na ustrb latencija tj brzina komunikacije izmedju recimo procesora ( grafike )i memorije.

npr. neke od latencija

RAS-to-CAS delay (tRCD) The RAS-to-CAS delay occurs between the time a row is activated and when the first read or write operation is performed.

CAS latency (CL) CAS latency refers to the delay between when a read operation is issued and when the data returned by that read is considered valid.

RAS precharge (tRP) The RAS precharge is the delay between when a precharge command is issued to close a row and when the next active command can be issued.

Active-to-precharge delay (tRAS) This latency actually spans several steps in the memory access process. The active-to-precharge delay refers to the minimum number of cycles that must elapse between an active and precharge command.

srecom amaterima kao sto smo mi to sve nimalo ( stabilnost, tacnost, brzine odziva ) nije vazno, pa ponekada vozimo sistem sa 8 cilindra i 16 ventila na 3 cilindra i 3 ventila.

al koga briga kad auto ide 250km/h do prve bandere ( fatal error )

vozi Misko !!!